AppRecs review analysis

AppRecs rating 3.6. Trustworthiness 70 out of 100. Review manipulation risk 26 out of 100. Based on a review sample analyzed.

★★★☆☆

3.6

AppRecs Rating

Ratings breakdown

5 star

40%

4 star

20%

3 star

20%

2 star

0%

1 star

20%

What to know

✓

Low review manipulation risk

26% review manipulation risk

✓

Credible reviews

70% trustworthiness score from analyzed reviews

✓

Good user ratings

60% positive sampled reviews

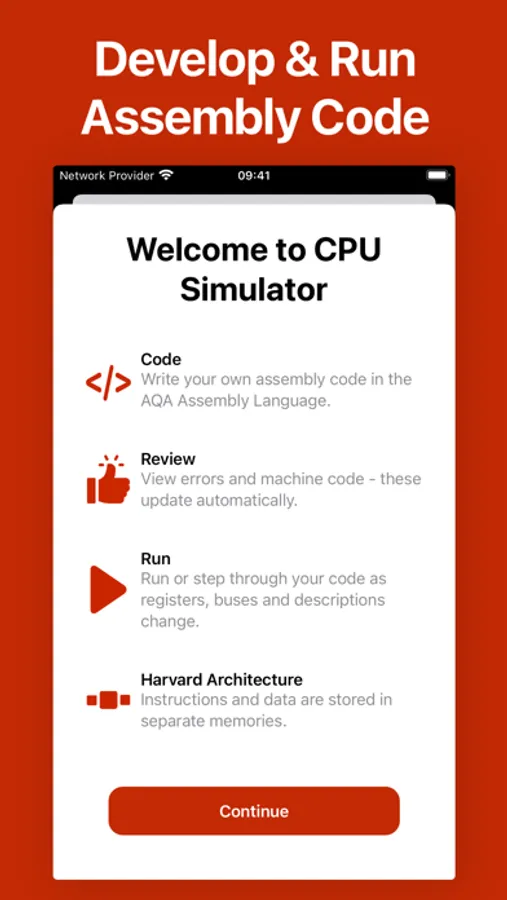

About CPU Simulator

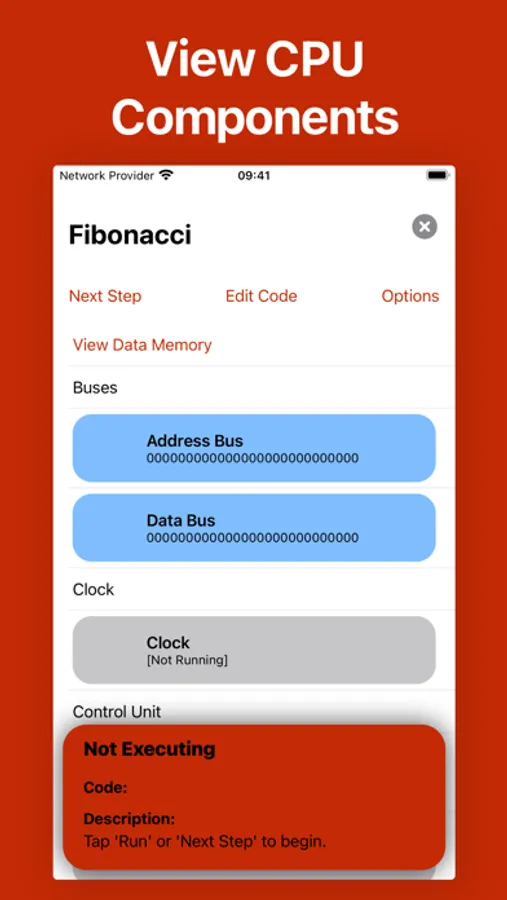

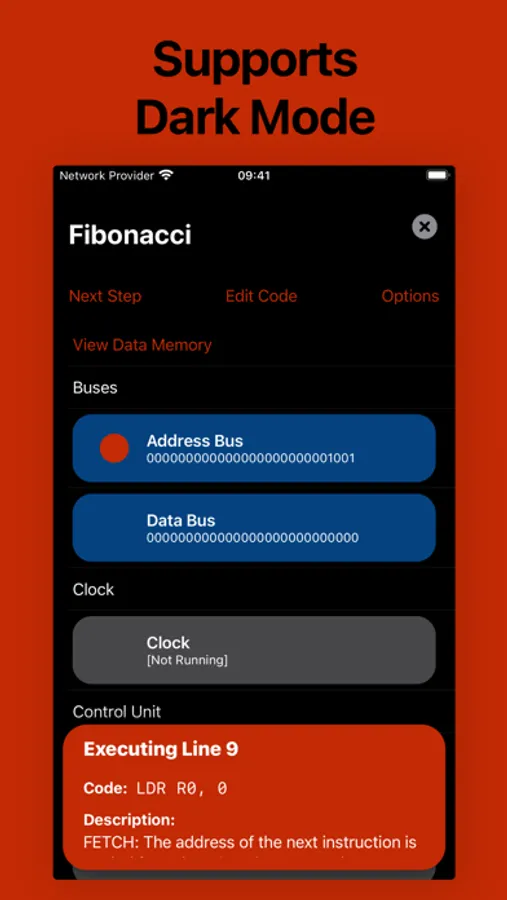

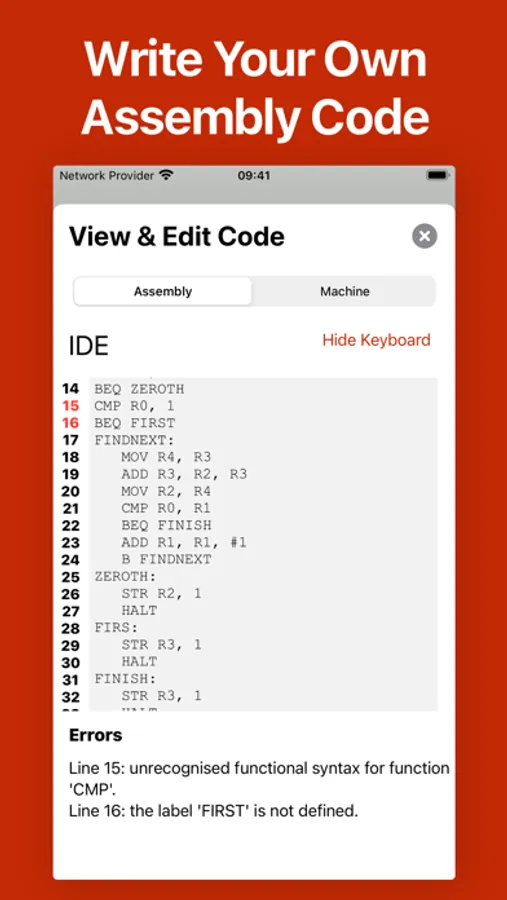

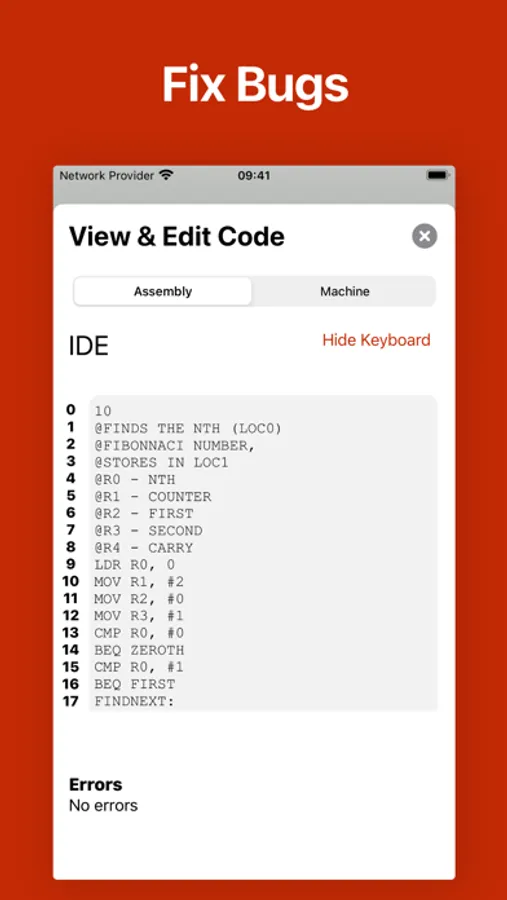

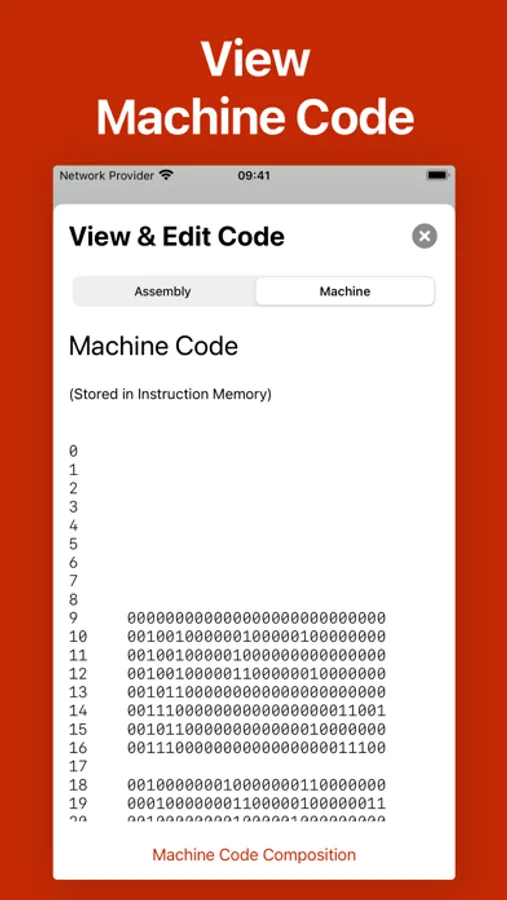

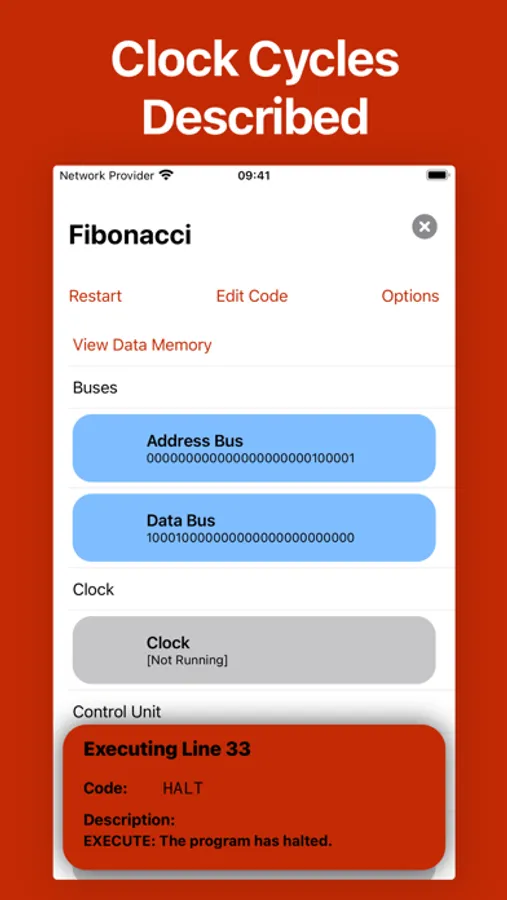

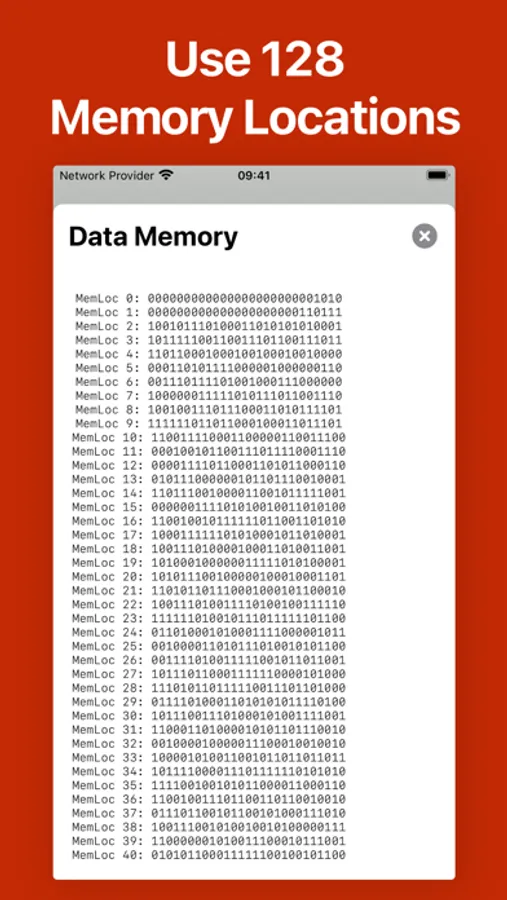

An interactive interface shows the components of the CPU, their contents, a description of what has changed in one clock cycle, an IDE to develop assembly code, an interface to view corresponding machine code, an interface to change preferences and more.

Components you can track:

• Address Bus

• Data Bus

• Clock

• Program Counter (PC)

• Current Instruction Register (CIR)

• Memory Address Register (MAR)

• Memory Buffer Register (MBR)

• 128 General Purpose Registers

• Arithmetic Logic Unit (ALU)

• Status Register

• 128 Data Memory Locations

• Instruction Memory

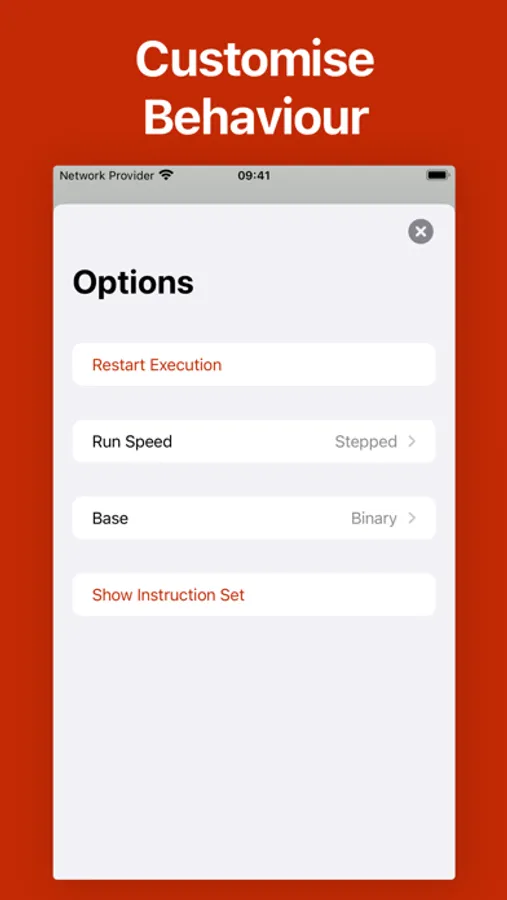

Options you can change:

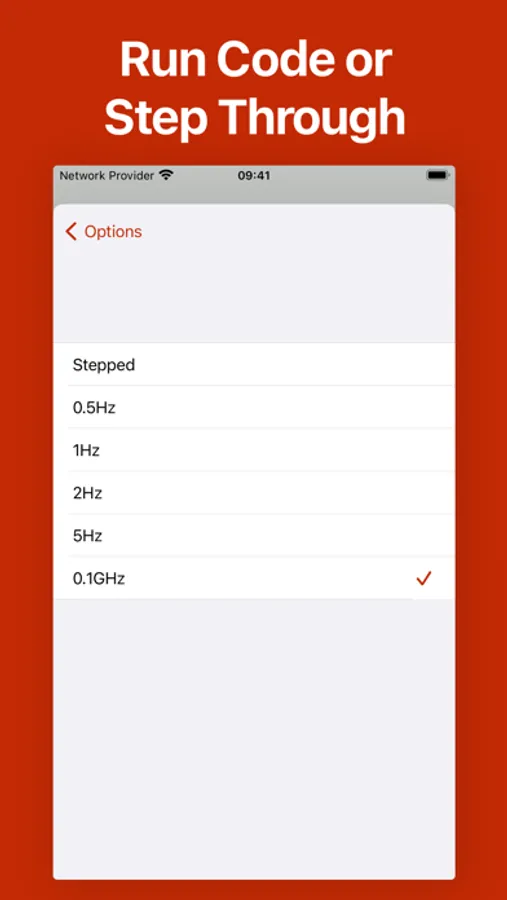

• Run Speed (including stepped mode)

• Number Base

This is a document-based application which means that you can create and run an unlimited number of unique simulations, save and share them.

This app is primarily intended to help teach ‘4.7.3.2 The Fetch-Execute cycle and the role of registers within it’ of the AQA A-Level specification, using the Harvard Architecture.

CPU Simulator Screenshots

Tap to Rate:

Reviews for CPU Simulator

ecolesthecreator

Cool app

Please consider open sourcing!!! The community can help maintain and add new features

IssacS1

Branching Operations don’t work

Hope to see some updates, Please update! Nicely formatted app with pretty good visual appeal to it, but I’ve noticed that the app almost always crashes when using branching operations within the code.